### $\mathsf{EMUL}-\mathsf{MICROBLAZE}-\mathsf{PC}^\mathsf{TM}$

### Getting Started Guide

Edition 4

© ICE Technology All rights reserved worldwide.

### Contents

| Warranty Information                                              |      |  |  |  |  |

|-------------------------------------------------------------------|------|--|--|--|--|

| European CE Requirements                                          | vi   |  |  |  |  |

| User Responsibility                                               | vi   |  |  |  |  |

| Special Measures for Electromagnetic Emission Requirements        | vi   |  |  |  |  |

| System Requirements                                               | vi   |  |  |  |  |

| Warnings                                                          | vii  |  |  |  |  |

| About This Guide                                                  | viii |  |  |  |  |

| 1                                                                 |      |  |  |  |  |

| Overview of the EMUL–MICROBLAZE–PC Emulator System                | 1    |  |  |  |  |

| Hardware                                                          | 1    |  |  |  |  |

| Software                                                          | 1    |  |  |  |  |

| 2                                                                 |      |  |  |  |  |

| Installing the Hardware                                           | 2    |  |  |  |  |

| USB Driver                                                        | 2    |  |  |  |  |

| Power Supply                                                      | 2    |  |  |  |  |

| InstallationInstructions                                          | 3    |  |  |  |  |

| 3                                                                 |      |  |  |  |  |

| Installing the Seehau Software                                    | 5    |  |  |  |  |

| Installing the Seehau Software From the CD                        | 5    |  |  |  |  |

| Installing the MicroBlaze EDK Software From the Xilinx EDK CD     | 5    |  |  |  |  |

| Downloading and Installing the Seehau Software From the Internet  | 6    |  |  |  |  |

| 4                                                                 |      |  |  |  |  |

| Configuring the Seehau Software                                   | 7    |  |  |  |  |

| Selecting to Automatically Start the Seehau Configuration Program | 7    |  |  |  |  |

| 8  |

|----|

| 8  |

| 10 |

| 11 |

| 11 |

| 11 |

| 13 |

| 13 |

| 13 |

| 13 |

|    |

| Running Program Examples   |    |  |  |  |

|----------------------------|----|--|--|--|

| Using The Trace            | 17 |  |  |  |

| Buttons Common to All Tabs | 17 |  |  |  |

| Events Tab                 | 17 |  |  |  |

| Trace Display Window       | 18 |  |  |  |

| 19 |

|----|

| 19 |

| 19 |

| 19 |

| 19 |

| 20 |

| 20 |

| 20 |

| 20 |

| 21 |

| 21 |

| 21 |

| 21 |

| 22 |

|    |

| Building a Project                                   | 23 |  |

|------------------------------------------------------|----|--|

| Building a Single Project                            | 23 |  |

| Building All Projects                                | 23 |  |

| Forcing a Build of a Single Project                  | 23 |  |

| Forcing a Build of All Projects                      | 23 |  |

| Forcing a Build of a Selected File                   | 23 |  |

| JTAG TROUBLESHOOTER                                  | 24 |  |

| JTAG TROUBLESHOOTER – WHEN SEEHAU DOES NOT START     | 24 |  |

| Start JTAG TROUBLESHOOTER                            | 25 |  |

| Starting Seehau with the Right Data                  | 26 |  |

| First time from Config:                              | 26 |  |

| 8                                                    |    |  |

| Using MicroBlaze Trace                               | 27 |  |

| Events Tab                                           | 27 |  |

| Trigger Conditions                                   | 28 |  |

| Program Address Trigger Condition                    | 28 |  |

| Register Write Trigger Condition                     | 28 |  |

| Probe Pins Channel A [70] Trigger Condition          | 28 |  |

| Probe Pins Channel B[310] Trigger Condition          | 28 |  |

| Post Trigger Count                                   | 29 |  |

| Break on Trace Stop                                  | 29 |  |

| Buttons Common to All Tabs                           | 29 |  |

| Trace Display Window                                 | 29 |  |

| 0                                                    |    |  |

| BlazeGen for EDK 6.2 Projects                        | 33 |  |

| BlazeGen                                             | 33 |  |

| Compiling Programs from XPS for use with Nohau Tools | 39 |  |

|                                                      |    |  |

| Using BlazeGen to Added DebugTrace Module            | 45 |  |

| Working with Platform Studio 6.1 & BlazeGen                              | 45 |

|--------------------------------------------------------------------------|----|

| Make a Quick Project Using Xilinx's Platform Studio and Nohau's BlazeGen | 45 |

| Working with Platform Studio 6.2 & BlazeGen                              | 51 |

| Make a Quick Project Using Xilinx's Platform Studio and Nohau's BlazeGen | 51 |

|                                                                          | 58 |

Index

### **Product Notes**

### Warranty Information

The pod board is sold with a one-year warranty starting from the date of purchase. The defective component under warranty will either be repaired or replaced at Nohau's discretion.

Nohau's Seehau software is sold with no warranty, but upgrades can be obtained to all customers at the Nohau Web site: <u>http://www.icetech.com</u>.

Nohau makes no other warranties, express or implied, including, but not limited to the implied warranties of merchantability and fitness for a particular purpose. In no event will Nohau be liable for consequential damages. Third-party software sold by Nohau carries the manufacturer's warranty.

### **European CE Requirements**

Nohau has included the following information in order to comply with European CE requirements.

### User Responsibility

The in-circuit debugger application, as well as all other unprotected circuits need special mitigation to ensure Electromagnetic Compatibility (EMC).

The user has the responsibility to take required measures in the environment to prevent other activities from disturbances from the debugger application according to the user and installation manual.

If the debugger is used in a harsh environment (field service applications for example), it is the user's responsibility to control that other activities cannot be disturbed in such a way that there might be risk for personal hazard/injuries.

### Special Measures for Electromagnetic Emission Requirements

To reduce the disturbances to meet conducted emission requirements it is necessary to place a ground plane on the table under the pod cable and the connected processor board. The ground plane shall have a low impedance ground connection to the host computer frame. The insulation sheet between the ground plane and circuit boards shall not exceed 1mm of thickness.

### System Requirements

### CAUTION

Like all Windows applications, the Seehau software requires a minimum amount of free operating system resources. The recommended amount is at least 40%. (This is only a guideline. This percentage might vary depending on your PC.) If your resources are dangerously low, Seehau might become slow, unresponsive or even unstable. If you encounter any of these conditions, check your free resources. If they are below 40%, reboot and limit the number of concurrently running applications. If you are unable to free at least 40% of your operating system resources, contact your system administrator or Nohau Technical Support at support@icetech.com.

The following are minimum system requirements:

- Pentium 1Ghz (Pentium III or faster is recommended)

- Single-Processor System

- USB Port

- Windows 2000 or XP

- Random Access Memory (RAM)

- For Windows 2000/XP: 256 MB

### Warnings

To avoid damage to the pod or to your target, do not connect the pod to your target when the target power is on.

Do not apply power to your system unless you are sure the target adapter is correctly oriented. Failing to do so can cause damage to your target.

When using the pod with a target, disable all pod resources that are duplicated on the target. Failure to disable the pod's resources can damage the pod or the target or both.

When installing a controller into a pod, never press on the chip body. Press only on the carrier or cover. Pressing on the chip might bend pins and cause short circuits.

### About This Guide

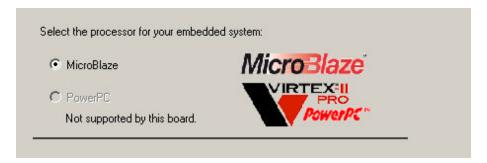

The EMUL–MICROBLAZE–PC is a PC-based hardware debugger for the MicroBlaze<sup>™</sup> Core, available for the Spartan<sup>™</sup>-II, Spartan<sup>™</sup>-II/E, Spartan<sup>™</sup>-III and Virtex<sup>™</sup>-II FPGA platforms from Xilinx<sup>®</sup>. This guide helps you to get started with the basics of setting up, configuring, and running the Seehau software and debugger.

The *EMUL–MICROBLAZE–PC Getting Started Guide* is intended for both novice and advanced users. This guide introduces the following tasks:

- Installing and configuring the Seehau software

- Installing the debugger hardware

- Starting the hardware and Seehau software

- Shutting down Seehau

To download an electronic version of this guide, do the following:

- 1. Open Nohau's home page at www.icetech.com.

- 2. Click Publications/Documents.

- 3. Click Nohau Manuals.

- **4.** Scroll down to EMUL–MICROBLAZE–PC. Then select EMUL–MICROBLAZE–PC to download a PDF version of this guide.

# Overview of the EMUL–MICROBLAZE–PC Emulator System

### Hardware

The basic hardware for the EMUL–MICROBLAZE debugger system is the EMUL–PC/USB–JTAG. At present, SeehauBLAZE supports the Spartan-II, Spartan-II/E and the Virtex-II FPGA platforms.

Refer to Chapter 2, "Installing the Hardware" for detailed hardware information overview.

### Software

The debugger is configured and operated by the SeehauBLAZE user interface. Seehau is a highlevel language user interface that allows you to perform many useful tasks, for example:

- Editing code in Source Window and building projects using the Nohau Project Manager and the supplied MicroBlaze GNU tools. The mb-gcc compiler, mb-as assembler and mb-ld loader/linker platform supplied by Nohau.

- Loading code into RAM, running, and stopping programs based on the MicroBlaze GNU tools. Additional documentation for programming the MicroBlaze core is available from Xilinx. This special version of the assembler outputs in ELF format specifically for the Nohau debugger. Contact Nohau Technical Support if you have questions.

- Modifying and viewing memory contents including general-purpose registers.

- Setting multiple software breakpoints that are placed in RAM.

- Set a trigger and display the trace.

## **2** Installing the Hardware

### **USB** Driver

When installing the USB device, you must install the Seehau software first before connecting the Nohau hardware (Refer to Chapter 3, "Installing the Seehau Software."). This allows the computer to recognize the proper driver for the hardware. The USB option is not supported by Windows 95 or NT.

The USB drivers are loaded as part of the Seehau software installation. The driver is located in the root directory of the installation CD. After installation, the driver is also located in the SeehauBLAZE subdirectory on your hard drive (C:\Nohau\SeehauBLAZE\). The system software should find and load the USB driver without your intervention.

### **Power Supply**

The EMUL–PC/USB–JTAG uses power supplied by the USB cable and the target board. The amount of power used by the pod from the target board is less than 100  $\mu$ A. When drawing power from the target board, the pod must draw from a 2.3V to 3.6V range. The power supplied by the target board drives the signal from the buffer on the pod through the 10-pin serial debug connector to the target board. The pod draws power from the target board through Pin 9 (Vdd).

Figure 1. EMUL-PC/USB-JTAG

### Note

The EMUL–PC/USB–JTAG is powered from the target. This allows the hardware to operate with a wide range of target voltages.

| Pin | Name     | Description                                              |  |  |  |

|-----|----------|----------------------------------------------------------|--|--|--|

| 1   | JTAG RST | JTAG Reset (not used for MicroBlaze) (Drive = Push/Pull) |  |  |  |

| 2   | /TMS     | Target slave select                                      |  |  |  |

| 3   | GND      | Ground                                                   |  |  |  |

| 4   | тск      | Target data clock                                        |  |  |  |

| 5   | Reserved | Reserved                                                 |  |  |  |

| 6   | Reserved | Reserved                                                 |  |  |  |

| 7   | /SRST    | System reset (Drive = Open-Drain)                        |  |  |  |

| 8   | TDI      | Target serial input                                      |  |  |  |

| 9   | Vdd      | Power                                                    |  |  |  |

| 10  | TDO      | Target serial output                                     |  |  |  |

The following table shows the signal layout of the connector:

### Installation Instructions

Refer to Figure 2 for a diagram of the connectors while following the installation instructions.

- 1. Make sure your target is powered off.

- **2.** Plug the 10-pin EMUL–PC/USB–JTAG serial debug connector onto your target's 10-header. This connector, supplies the signals needed to communicate with the EMUL–PC/USB–JTAG.

- 3. Power on your target.

#### Note

Exit Seehau and shut down the power to the target when the target is not in use.

The red wire indicates pin one on the 10-pin serial debug connector.

Figure 2. EMUL–MicroBlaze–PC/USB–JTAG with the 10-Pin Serial Debug Connector

Figure 3. Connections for the USB Cable and the Red Wire Pin 1

## **3** Installing the Seehau Software

Installing the Seehau Software From the CD

To install the Seehau software, do the following:

- 1. Locate your Seehau CD and insert the CD into your CD ROM drive. The installation process will start automatically.

- 2. Click Install Seehau Interface for EMUL-MicroBlaze-PC and follow the instructions that appear on your screen.

If the installation does not start automatically, you might have your Windows Autorun feature disabled. You will then need to do one of three things:

- Use Windows Explorer and navigate to the CD root directory. Double-click **Autorun.exe**. The Windows Install Shield will start the installation process.

- Right-click on the CD ROM symbol while running Windows Explorer and select **AutoPlay** to start the installation process.

- From the taskbar, select **Start**, then **Settings**. Click on **Control Panel**, then **Add/Remove Programs**, and then **Install**. The installation process will start when you select the correct path to the CD.

Installing the MicroBlaze EDK Software From the Xilinx EDK CD

In order to build programs using the Nohau Project Manager you need to install the MicroBlaze EDK software using the following:

- 1. Locate your EDK CD and insert the CD into your CD ROM drive. The installation process will start automatically.

- 2. Click Install the MicroBlaze EDK and follow the instructions that appear on your screen.

If the installation does not start automatically, you might have your Windows Autorun feature disabled. You will then need to do one of three things:

- Use Windows Explorer and navigate to the CD root directory. Double-click **Autorun.exe**. The Windows Install Shield will start the installation process.

- Right-click on the CD ROM symbol while running Windows Explorer and select **AutoPlay** to start the installation process.

• From the taskbar, select **Start**, then **Settings**. Click on **Control Panel**, then **Add/Remove Programs**, and then **Install**. The installation process will start when you select the correct path to the CD.

Downloading and Installing the Seehau Software From the Internet

- 1. Go to the Nohau web site (http://www.icetech.com/). Click **Downloads**. The Nohau Software Downloads page opens.

- 2. Click Current Seehau Software. The Seehau Software Status page opens.

- **3.** Locate the EMUL–MICROBLAZE–PC product listing. There will be two listings, one for documentation and one for software.

- 4. Click Information and Download (Seehau).

- **5.** Review the information on the page.

- 6. Click Yes I Want to Download. A Customer Information Form page opens. Complete this form, then click Proceed. (You have the option to download more than one product.) A verification page opens with the information you have just entered. If all information is correct, select SEND at the bottom of the page. A message will open that verifies your information has been sent.

- 7. Click Go to Download. The Available Download Areas page opens.

- 8. Click either option for a download site. The Nohau Software Updates page opens.

- 9. Click the EMUL–MICROBLAZE–PC link.

- **10.** Click the MicroBlaze.exe link. The application will start downloading. Remember which directory has this downloaded file.

- **11.** Following the download, go to the directory, which has the downloaded file. Click the Micro-Blaze.exe file and follow the installation instructions.

After installing the Seehau software, the **Setup Complete** dialog boxes appears that allows you to view the Readme.txt file and/or launch the SeehauBLAZE configuration.

### Note

You must launch the SeehauBLAZE configuration before running the Seehau software.

# Configuring the Seehau Software

Selecting to Automatically Start the Seehau Configuration Program

After installing Seehau, it is recommended that you automatically start the Seehau Configuration program. Do the following steps before starting Seehau:

- 1. From the Setup Complete dialog box, select Launch SeehauBLAZE Configuration.

- 2. Click Finish.

If you do not select to automatically start the Seehau Configuration Program, do the following:

From the Start menu, select Programs.

Select SeehauBLAZE. Then click Config to open the Emulator Configuration window displaying the Connect tab (Figure 4).

| Emulato | r Configuration                                 |        |      |       |                       |        |

|---------|-------------------------------------------------|--------|------|-------|-----------------------|--------|

| Connect | ŧ                                               |        |      |       |                       |        |

| 1       | SPI                                             | E way  |      |       |                       |        |

| 2       | Select Emulator Connect<br>Universal Serial Bus | on:    |      |       |                       |        |

| 3       | Select Processor:<br>MicroBlaze_VX2_1000        |        |      |       |                       |        |

| 4       | What is your Trace Type?<br>Trace(yes)          | )      |      |       |                       |        |

| ,       |                                                 |        |      |       |                       |        |

|         |                                                 |        |      |       |                       |        |

|         |                                                 | Cancel | Help | About | <b>←</b> <u>P</u> rev | Next 🔶 |

Figure 4. Emulator Configuration Window Displaying the Connect Tab

#### Note

You do not need the hardware connected at this time

### Configuring the Communications Interface

### Connect Tab

The graphical user interface for this tab is divided into four regions. Do the following in each region:

- 1. Region 1—Communications Interface: Displays the USB-SPI communications interface for the MicroBlaze pod or the Xilinx Parallel Cable option.

- 2. Region 2—Select Emulator Connection: No action required. Default is Universal Serial Bus.

- Region 3—Select Processor: Default is MicroBlaze\_SPARTAN\_2E\_200 for the Spartan-II/E on the Nohau MicroBlaze evaluation board. Select MicroBlaze-VX2-1000 for the Virtex-II or the Virtex-II PRO. Depending on your version of software you may have to select the this option also for the Spartan-III. Otherwise, Select Spartan-III for the Spartan-III.

- 4. Region 4—What is your Trace Type?: Select Trace (Yes). Default is Yes.

- 5. Click Next. The Hdw Config tab opens (Figure 5).

| diaton<br>dia Con | 1.51                        |      |           |            |      |   |        |        |

|-------------------|-----------------------------|------|-----------|------------|------|---|--------|--------|

| ONAU              | Processor<br>MicroBlaze_VX2 | 1000 |           |            |      |   |        |        |

|                   | her Recet(ms)               | 0    | - 17 B    | leset High | 0    |   |        |        |

| Itag Ch           | hain                        |      |           |            |      |   |        |        |

| Numbe             | er Of Jtag Devices          | 2    |           |            |      |   |        |        |

|                   |                             |      | 202000    | - 1 L      |      |   |        |        |

|                   |                             |      | Configure | -          |      |   |        |        |

| Logic F           | File                        |      |           |            |      |   |        |        |

| 0.590             | not Load                    |      |           |            |      |   |        |        |

| -                 |                             |      |           |            |      |   |        |        |

| 2                 |                             |      |           | 100        |      |   |        |        |

|                   |                             |      |           |            |      |   |        |        |

|                   |                             | ç    | ancel     | Help       | Abou | 1 | + Brev | Einish |

Figure 5. Emulator Configuration Window Displaying the Hdw Config Tab

### Hardware Configuration Tab

The initial configuration settings are read from the Startup.bas file when the debugger initializes. After the initial startup and configuration of Seehau, the configuration parameters are saved in the Startup.bas file (located in the Macro subdirectory). The next time the emulator is started, the configuration parameters are read in from the Startup.bas file and compared with the default parameters on the chip.

- **Processor**: Shown for reference only. This is the selected processor. If you need to change the pod type, click **Prev**.

- Delay after Reset(ms): Used to set the length of time Seehau asserts reset.

- **Reset High**: Used to set the type of reset configured in the MicroBlaze core. The default is active high.

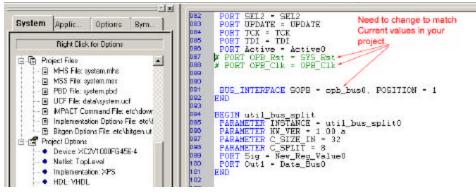

- JTAG Chain: Used to configure the JTAG chain setup so that Seehau can talk to the Micro-Blaze core in the current scan chain. (See Figure 6). With versions of Seehau that have been built after May 20, 2004 the software will automatically try to detect the devices in the scan chain and automatically fill in these values.

- Logic File: Used to configure the initial bit stream to be loaded into the FPGA.

When you click **Finish**, Seehau starts to load. For more information about starting Seehau, see the "Starting Seehau" section at the end of this chapter.

|                                                    | <u> </u>                              |

|----------------------------------------------------|---------------------------------------|

| 2 •                                                |                                       |

| Instruction Reg Size<br>8 - Bits IR<br>5 - Bits IR | Cancel<br><u>H</u> elp                |

|                                                    | 2 Instruction Reg Size<br>8 - Bits IR |

Figure 6. Emulator Configuration Window Configure JTAG Chain Button

- Number of Devices: Used to set the total number of devices in the scan chain

- Active Device Position: Used to set where the MicroBlaze core is in scan chain relationship.

• **Device (x) Bypass**: Used to set the "Instruction Register length" of each device in the chain.

### Configuring the Emulator Options From Within Seehau

From Seehau, open the Emulator Configuration window. From the **Config** menu select **Emulator**.

The Emulator Configuration window contains two tabs. When selected, each tab allows you to set the following options:

Hdw Cfg: Set up emulator hardware options.

Misc Setup: Select reset options.

### Buttons Common to All Tabs

- **OK**: Saves the settings for the tab and exits the dialog box.

- **Apply**: Saves the settings for the tab.

- **Cancel**: Exits without saving the settings for the dialog box.

- **Help**: Displays the Seehau Help file.

- **Refresh**: Allows you to retrieve and view the current emulator hardware configuration settings.

Hardware Configuration Tab

- **Processor**: Shown for reference only. This is the selected processor. If you need to change the pod type, click **Prev**.

- **Delay after Reset(ms)**: Used to set the length of time Seehau asserts reset.

- **Reset High**: Used to set the type of reset configured in the MicroBlaze core. The default is active high.

- **JTAG Chain**: Used to configure the JTAG chain setup so that Seehau can talk to the Micro-Blaze core in the current scan chain. (See Figure 6).

- Logic File: Used to configure the initial bit stream to be loaded into the FPGA.

| dia Corl | Configuration      |        |          |            |  |  |

|----------|--------------------|--------|----------|------------|--|--|

|          | Processor          |        |          |            |  |  |

| понач    | MicroBlaze_VX      | 2_1000 |          |            |  |  |

| )elay al | ter Recet(ms)      | 0      |          | Reset High |  |  |

| Jtag Ch  | hain               |        |          |            |  |  |

| Numbe    | er Of Jtag Devices | E      | 2        |            |  |  |

|          |                    | 18     |          |            |  |  |

|          |                    |        | Conligue |            |  |  |

|          |                    |        |          |            |  |  |

| Logic F  | le                 |        |          |            |  |  |

| F 00     | not Load           |        |          |            |  |  |

| -        |                    |        |          |            |  |  |

| 1        |                    |        |          |            |  |  |

| -        |                    |        |          |            |  |  |

|          |                    |        |          |            |  |  |

Figure 7. Emulator Configuration Window Displaying the Hdw Config Tab

| Emulator Configuration<br>Hdw Config Misc Setup |                         |                      |

|-------------------------------------------------|-------------------------|----------------------|

| ✓ Reset chip after load file                    | Override at Reset       |                      |

| <u>QK</u> <u>Apply</u>                          | <u>C</u> ancel <u>H</u> | Help <u>R</u> efresh |

Figure 8. Emulator Configuration Window Displaying the Misc Setup Tab

Miscellaneous Setup Tab

The **Misc Setup** tab () is accessible only after the initial software configuration.

- **Reset chip after load file**: Sets the MicroBlaze core to issue a reset after the code is loaded.

- Override at Reset

- The Program Counter option selects the value that the program counter will be set to after a reset. Enter the program counter value in the box.

- The Stack Pointer option selects the value that the stack pointer will be set to after a reset. Enter the stack pointer value in the box.

When the target is powered on, the EMUL–PC/USB–JTAG pod is powered by the target through a diode.

When powering down, turn off the target first and then the pod (the pod receives its power through the USB cable so the PC must be powered down to power off the pod.)

Starting Seehau

Demo Mode

- 1. Double-click the Demo icon. The Seehau main window opens (Figure 9). Seehau will load its configuration from the Startup.bas file. Notice that the word macro is displayed in red at the bottom of the main window while Startup.bas is running.

- 2. When the software startup is complete, you can position and resize the main window to your preference. At this time, you will need to load code.

- 3. To open new windows, from the **New** menu click a window option.

Non-Demo Mode

To start Seehau, in the non-demo mode do the following:

1. Double-click the SeehauBLAZE icon. The Seehau main window opens (Figure 9). Seehau will load its configuration from the Startup.bas file. Notice that the word macro is displayed in red at the bottom of the main window while Startup.bas is running.

- 2. When the software startup is complete, you can position and resize the main window to your preference. At this time, you will need to load code.

- 3. To open new windows, from the **New** menu click a window option.

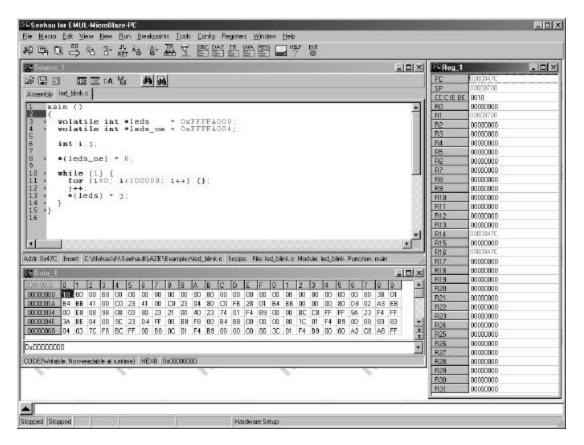

Figure 9. Seehau for EMUL-MICROBLAZE-PC

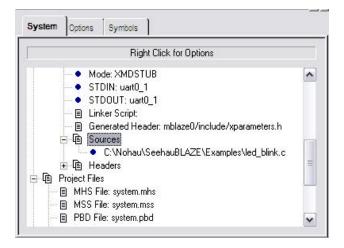

# **5** Running Program Examples

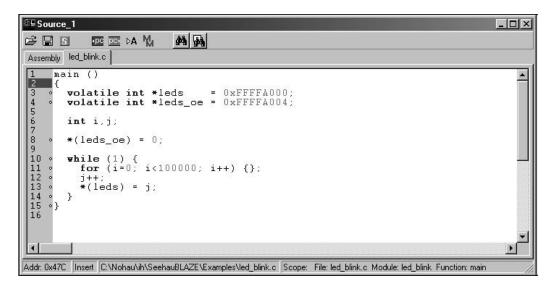

Nohau provides a C program example called led\_blink located at: C:\Nohau\SeehauBLAZE\Examples\led\_blink.out)

### Note

The C programs do not have a jump to main when XMD\_STUB is used. Using the Misc Setup tab of the Emulator Configuration window, set the PC to main and the stack pointer to **700h** before stepping into the C programs. Once you have done this, step into the C source code by pressing the Source Step Into button on the Seehau Speedbar.

Start Seehau by following the instructions in the "Starting Seehau" section in Chapter 4. Then do the following to run the test program:

- 1. Resize the windows on your screen, but do not add the Watch window.

- 2. From the File menu select Load Code. The Open dialog box opens (Figure 10).

- 3. Select one of the program example files for your controller.

| Open                                         |                                   |   |       | ?×                     |

|----------------------------------------------|-----------------------------------|---|-------|------------------------|

| Look jn: 🖂                                   | Examples                          | • | + 🗈 c | ∲ <b>⊞</b> ∙           |

| ib<br>ied_blink.                             |                                   |   |       |                        |

| File <u>n</u> ame:<br>Files of <u>type</u> : | led_blink.out<br>OUT Files(*.out) |   |       | <u>O</u> pen<br>Cancel |

Figure 10. Open Dialog Box Displaying the Program Example Directories

Figure 11. Program Example in Source Only

- 4. Highlight the program example file and click **Open**. The source file automatically displays the program example in source only (Figure 11).

- **5.** To single-step in mixed mode, click the Assembly Step Into or Step Over button. You will see the assembly code mixed in with the associated source lines (Figure 12).

- 6. To single-step in source only mode, first click the Source window. Select the led\_blink.c tab. Right-click to verify that mixed mode is cleared. Then point to the Setting sub-menu item, and select Lock Tabs.

| Gource_1<br>🖃 S 🔤 🗠 🕅 🎆                            |          |               |   |

|----------------------------------------------------|----------|---------------|---|

| embly led_blink.c                                  |          |               |   |

| •{                                                 |          |               |   |

|                                                    | : addi   | r1,r1,#0xFFE8 |   |

| 00000480: 140061FA                                 |          | r19,r1,#0x14  |   |

| 00000484: 00006102<br>• <b>volatile int *</b> leds | add      | r19,r1,r0     |   |

|                                                    |          |               |   |

| 00000488: 00A06020                                 |          |               |   |

| 0000048C: 040073F8                                 |          |               |   |

| <ul> <li>volatile int *leds_oe</li> </ul>          | = 0xFFFF | A004;         |   |

| 00000490: 04A06020                                 | addi     | r3,r0,#0xA004 |   |

| 00000494: 080073F8                                 | swi      | r3,r19,#0x8   |   |

| int i,j;                                           |          |               |   |

| Inc I, J,                                          |          |               |   |

| <pre> • *(leds_oe) = 0; </pre>                     |          |               |   |

|                                                    | lwi      | r3,r19,#0x8   |   |

| 0000049C: 001800D8                                 | sw       | r0,r0,r3      |   |

|                                                    |          |               |   |

| • <b>while</b> (1) {                               | 1        | #0430         |   |

|                                                    |          |               | • |

|                                                    |          |               |   |

Figure 12. Program Example in Mixed Mode

### Using The Trace

The EMUL-MICROBLAZE-PC-Pro provides a 128K deep trace with a trigger, post trigger count and break control.

The **Event Configuration** window is selected from the **Config** menu select **Trace**. The Event Configuration window opens displaying the **Events** tab (Figure 13).

Buttons Common to All Tabs

- **OK**: Saves the settings for the tab and exits the dialog box.

- **Apply**: Saves the settings for the tab.

- **Cancel**: Exits without saving the settings for the dialog box.

- **Help**: Displays the Seehau Help file.

- **Refresh**: Allows you to retrieve and view the current event configuration settings.

#### **Events Tab**

- Trigger Condition

- The value in the **Address** is the value that trigger is set to.

- The **Trigger Enable** activates the trigger.

- **Post Trigger Count**: The frames to capture after the trigger condition has occurred. When the Post Trigger Count is zero, this will indicate the trigger has occurred.

- **Break on Trace Stop**: When checked will cause emulation to break when the trace has stopped.

| Event Config                    | uration             |        |      |                 |      |  |

|---------------------------------|---------------------|--------|------|-----------------|------|--|

| Events                          |                     |        |      |                 |      |  |

| Post Trigger (<br>0<br>Break on | Count<br>Trace Stop |        |      |                 |      |  |

|                                 |                     |        |      |                 |      |  |

| <u></u> K                       | Apply               | Cancel | Help | <u>R</u> efresh | <br> |  |

Figure 13. Event Configuration Window Displaying the Events Tab

### Trace Display Window

The **Trace Display** window is used to display the results of the trace capture. The default fields displayed from right to left are the **Frame**, **Address**, **Opcode**, **Instruction** and **Symbol**.

The **Trace Display** window can display trace only (assembly), mixed (source and assembly) or source only. The mixed mode is shown in (Figure 14).

| 📴 Trace  | e_1            |                  |              |             |        |

|----------|----------------|------------------|--------------|-------------|--------|

| Frame    | Address        | Opcode           | Instr.       |             | Symbol |

| -22      | 434            | 0000E1C4         | lhu          | r7,r1,r0    |        |

| -21      | 438            | OEOOCOF4         | shi          | r6,r0,#0xE  |        |

| -20      | 43C            | OAOOEOF4         | shi          | r7,r0,#0xA  |        |

| -19      | 4C0            | 01008320         | addi         | r4,r3,#0x1  |        |

| -18      | 4C4            | 080093F8         | swi          | r4,r19,#0x8 |        |

| -17      | 4C8            | DCFF00B8         | bri          | #0x4A4      |        |

| -16      | j++;           |                  |              |             |        |

| -16      | 4CC            | OC0073E8         | lwi          | r3,r19,#0xC |        |

| -15      | 4DO            | 01008320         | addi         | r4,r3,#0x1  |        |

| -14      | 4D4            | 0C0093F8         | swi          | r4,r19,#0xC |        |

| -13      | *(leds)        | = j;             |              |             |        |

| -13      | 4D8            | 009860C8         | lw           | r3,r0,r19   |        |

| -12      | 4DC            | OC0093E8         | lwi          | r4,r19,#0xC |        |

| -11      | 4E0            | 001880D8         | sw           | r4,r0,r3    |        |

| -10      | 4F4            | 08000FB6         | rtsd         | r15,0x8     | -      |

| -9       | 4F8            | 08000000         | nop          |             |        |

| <u> </u> |                |                  |              |             |        |

| MIXED g  | jot frames Fra | ames:29(-29:-1), | Trig Count:0 |             | 10     |

Figure 14. Trace Display in Mixed Mode

# **6** Using the Nohau Project Manager

### Overview

The Nohau Project Manager is an external application that allows you to launch compilers and linkers for processing source files and linker command files as specified in the workspace. The Project Manager gives you different options of how to build the source files and automatically load the final object file into the emulator. This chapter describes how to:

- Create a workspace.

- Add a project to the workspace.

- Add files to the project.

- Specify file settings for each of the source files (can be done as a group or individually).

- Test the project settings.

- Open the source file in the Seehau Source window.

### Accessing the Nohau Project Manager

Accessing the Nohau Project Manager can be done in one of the following ways:

- Start the Windows Explorer utility and go to C:\Nohau\SeehauBLAZE. Double-click NPrjMngr.exe.

- Within Seehau, from the **Tools** menu, select **Open Project Manager**.

The Nohau Project Manager window opens.

### Working with Workspaces

### Adding a New Workspace

- 1. From the File menu, select New Workspace. (You can also click the New Workspace button on the toolbar). This opens the New Workspace dialog box.

- 2. Type in the name of the new workspace in the Workspace name text field.

- **3.** Click **OK**. The new workspace name appears in the left side of the Nohau Project Manager window. (In Figure 15, the example is **My Workspace**.)

| 🕮 Nohau Project Manager          |                                            |

|----------------------------------|--------------------------------------------|

| <u>File Settings Build H</u> elp |                                            |

| ∎e∎∎X+-                          | <b>P</b>                                   |

| ****                             |                                            |

| ⊡Blaze1<br>I MyTest              | C.\Nohau\SeehauBLAZE\Examples\led_blink.c_ |

|                                  |                                            |

|                                  |                                            |

Figure 15. Nohau Project Manager Window

### Opening a Workspace

- 1. To open a workspace from the File menu, select **Open Workspace**. (You can also click the Open Workspace button on the toolbar). This opens the **Open** dialog box.

- 2. Select the file C:\Nohau\SeehauBLAZE\Examples\Blaze1.npr, click Open. The name of the selected file appears in the left side of the Nohau Project Manager window.

### Saving a Workspace

- 1. To save a workspace from the File menu, select Save Workspace. (You can also click the Save Workspace button on the toolbar.) This opens the Select Directory dialog box.

- 2. When you have placed your workspace file where you want it, click **OK** to save the file and exit the dialog box.

### Working with Projects

Adding a New Project

- 1. Click on the workspace name in the left side of the Nohau Project Manager window. (In Figure 15, the example is **Blaze1**.)

- 2. From the File menu, select Add New Project. (You can also click the New Project button on the toolbar). This opens the New Project dialog box.

- 3. Type in the name of the new project in the **Project Name** text field.

- 4. Click OK. The new project name appears in the left side of the Nohau Project Manager window. (In Figure 15, the example is **My Test**.)

Removing a Project

- **1.** Select (highlight) the project name.

- 2. From the File menu select **Remove Project**. (You can also click the Remove Project button on the toolbar).

- 3. A message box opens asking you Do you want to remove project (file name)? Click Yes to remove the selected file, or Cancel to close this box.

Adding a File to the Project

- **1.** Select (highlight) the project name.

- 2. From the File menu select Add File to Project. (You can also click the Add File to Project button on the toolbar). This opens the **Open** dialog box.

- 3. When you have located the .c file you want to add, click Open. The name of your selected file appears in the right side of the Nohau Project Manager window. (In Figure 15, the example is C:\Nohau\SeehauBLAZE\Examples\led\_blink.c.)

### Removing a File from the Project

- Select (highlight) the file name. (In Figure 15, the example is C:\Nohau\SeehauBLAZE\Examples\led\_blink.c.)

- 2. From the File menu select Remove File from Project. (You can also click the Remove File from Project button on the toolbar).

- **3.** A message box opens asking you **Do you want to remove file (file name)?** Click **Yes** to remove the selected file, or **Cancel** to close this box.

### Changing the Workspace Settings

- 1. From the Settings menu select Workspace Settings. The Workspace Settings dialog box opens.

- 2. Select one of the compiler-specific tools, this is mb-gcc.exe for MicroBlaze. This file translates the errors generated by the compiler into a format that allows you to view the errors in the Source window. If your compiler does not have a Nohau error-translating tool, contact Nohau Technical Support at support@icetech.com.

You can also write your own error-translating tool. The .exe file that you create reads the file as a command line parameter when you launch the tool. This file name is displayed in the **Report File** text field in the **File Settings** dialog box (Figure 16). To open this dialog box from the **Settings** menu, select **File Settings**.

| 🖫 Nohau Project Manager 📃 🗖 🗙                         |

|-------------------------------------------------------|

| <u>File S</u> ettings <u>B</u> uild <u>H</u> elp      |

| 🗈 🗠 🖬 🖹 🗙 + = 🌄                                       |

| ****                                                  |

| Blaze1      C:\Nohau\SeehauBLAZE\Examples\led_blink.c |

| MyTest                                                |

| File Settings                                         |

| Executable                                            |

| C:\MicroBlaze\bin\gnu\mb-gcc.exe                      |

|                                                       |

| Pre Parameters -g -v -mxl-gp-opt -xl-mode-xmdstub     |

| Post Parameters -o ledblink.out lib/libc.a lib/libm.a |

| Output File                                           |

| C:\Nohau\ih\SeehauBLAZE\Examples\led_blink_jack.ou    |

| Load into Seehau                                      |

|                                                       |

| Report File                                           |

| C:\Nohau\ih\SeehauBLAZE\Examples\led_blink.lst        |

| Build Status                                          |

| C Exclude From Build                                  |

| C Build Always                                        |

|                                                       |

| <u>Q</u> k <u>C</u> ancel                             |

Figure 16. File Settings Dialog Box

The error-translating tool parses the file for error messages. It then appends them to the Cmperror.log file for Seehau to read it. The .log file should be in the following format: **Filename#linenumber#the original error text**

With this convention, the Nohau tool supports most compilers and message outputs.

### Changing the File Settings

- Select (highlight) the file name. (In Figure 16, the example is C:\Nohau\SeehauBLAZE\Examples\led\_blink.c.)

- 2. From the Settings menu select File Settings. (You can also click the File Settings button on the toolbar.) This opens the File Settings dialog box (Figure 16).

You can now choose the functions you wish to perform, such as entering post parameters, creating an executable path to process the file, creating an output file name and a report file name. You can also choose to load the output file into Seehau, exclude the file from the build, or specify if it should be the default file. Selecting the **Build** option ensures the source file will be built if the date of the output file is older than the date of the source file.

For example, if you want to compile a .c file that is called Test.c, the executable field should contain the path to the compiler. The **Pre Parameter** field contains command line parameters to the compiler that appear before the file name Test.c. The **Post Parameter** field specifies command line parameters that appear after the file name Test.c. The **Output File** filename is Test.obj. The **Report File** filename is Test.lst.

If the file settings are specified for the linker command file, the **Output File** name is Test.omf or Test.hex and the **Load Into Seehau** option should be selected. This instructs Seehau to load the linked output file into the emulator.

### **Building a Project**

**Building a Single Project**

- 1. Select (highlight) the project.

- 2. From the Build menu select Build Selected Project (Make). (You can also click the Build Selected Project(Make) button on the toolbar.)

### Building All Projects

From the **Build** menu select **Build All Projects (Make)**. (You can also click the Build All button on the toolbar.)

Forcing a Build of a Single Project

- **1.** Select (highlight) the project.

- 2. From the **Build** menu select **Rebuild Selected Project**. (You can also click the Rebuild Selected Project button on the toolbar.)

### Forcing a Build of All Projects

From the **Build** menu select **Rebuild All Projects**. (You can also click the Rebuild All button on the toolbar.)

Forcing a Build of a Selected File

- **1.** Select (highlight) the file.

- 2. From the **Build** menu select **Build Selected File**. (You can also click the Build Selected File button on the toolbar.)

When powering up, connect the USB cable and then power on the target.

ERROR CONDITION: If you ever note that the led indicator (Blue or Green) on the Pod is continuously on when you are not running Seehau or when you are not actively interacting with the target, it is an error condition likely caused by an erroneous power sequence. To correct the situation, power down the target then disconnect the USB cable to the pod wait 20 seconds. Then reconnect the USB cable followed by power up of the board. If there has been no damage to the pod, the pod led indicator will be off.

JTAG TROUBLESHOOTER - WHEN SEEHAU DOES NOT START

After a period of about a minute of trying to load, one of several messages like the one below will appear. It is an error reporting that communication to the FPGA was not established with the POD.

| Seehau - Unrecoverable Error                                                                       | X   |

|----------------------------------------------------------------------------------------------------|-----|

| Seehau will attempt to exit without saving any settings!                                           | ^   |

| The software has failed to communicate with the pod.<br>Clicking 'Help' may give more information. |     |

| Send using USB failed.<br>Resynchronize, Read Mon version<br>Buffer Size 66                        | III |

| Cmd: Cfg_InitPod1                                                                                  | ~   |

| Copy Troubleshoot OK Full Reset Help                                                               |     |

### Figure 17. Typical Error Message when Communication Fails

The message is a direct result of our not being sure what to specify in the JTAG scan chain. However on new boards, solder shorts or any number of conditions can cause this failure.

### Start JTAG TROUBLESHOOTER

| Verify USB Connection                                                              | Logic File                                 |  |

|------------------------------------------------------------------------------------|--------------------------------------------|--|

| I Using Trace                                                                      | Do not Load Logic                          |  |

| F Slow Jtag Clock                                                                  |                                            |  |

| Toggle TCLK                                                                        |                                            |  |

| T eggle TDI                                                                        | 🕫 Repeat Each Toggle 200 🚊                 |  |

| Toggle TMS                                                                         | Toggle Unit Stop                           |  |

| Reverse System Reset polarity<br>Reverse JTA5 Revet polarity                       |                                            |  |

| <ul> <li>Repeat Autodetect, zo you can m<br/>Autodetect JTAG scan chain</li> </ul> | eacure on TDO<br>Max Num Of Dev _6 _ ⊉ _ I |  |

| - 20 V0550 3                                                                       |                                            |  |

Select the **Troubleshoot** button to bring up the dialog box below:

#### Figure 18. TROUBLESHOOTER Control

- 1. Select **Verify USB** and note the result displayed on the bottom bar

- 2. Select **Toggle TCLK** 400 times and note result.

- 3. Select **Test Pod Power** and note result, which should be ok.

- 4. Select **Autodetect JTAG Scan Chain** and pull down the drop down box after it completes as shown in Figure 19.

| Verify USB Connection                                                                                                               | Logic File                                    |       |       |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------|-------|

| 🔲 Using Trace                                                                                                                       | 🖵 Do not Load Logic                           |       |       |

| 📕 Slow Jtag Clock                                                                                                                   |                                               |       |       |

| Toggle TCLK                                                                                                                         |                                               |       |       |

| Toggle TDI                                                                                                                          | Repeat Each Toggle 200                        |       |       |

| Toggle TMS                                                                                                                          | C Toggle Until Stop                           |       |       |

| Reverse System Reset polarity                                                                                                       |                                               |       |       |

| Reverse System Reset polarity<br>Reverse JTAG Reset polarity<br>Repeat Autodetect, so you can me<br>Autodetect JTAG scan chain      |                                               |       |       |

| Reverse JTAG Reset polarity     Repeat Autodetect, so you can me     Autodetect JTAG scan chain     found Devices(IDCode/Device/IR) | Max Num Of Dev 6                              |       |       |

| Reverse JTAG Reset polarity     Repeat Autodetect, so you can me     Autodetect JTAG scan chain     found Devices(IDCode/Device/IR) | Max Num Of Dev 6<br>05026093 : XC18V04 IR = 8 | About | Close |

#### Figure 19. TROUBLESHOOTER Control Data

Take out a piece of paper and write down the device ID, the number of bits in the instruction register and their relative position in the scan chain. For unknown devices, you must look them up on your schematics and consult data sheets from manufactures to determine their Instruction Register Lengths.

Close the troubleshooter program and return to programs ->SeehauBlaze->config. Repeat the procedure to start the Seehau Configuration Program, only this time with the correct data.

If you have a problem with this, ask for help so it doesn't take up too much of your lab time.

### Starting Seehau with the Right Data

First time from Config:

When you click **Finish** from **Config**, Seehau prompts you for a selection to start the emulator.

Select **Yes** and Seehau starts to load and program the FPGA configuration from the specified .bit file. When you exit Seehau the first time, you may choose to save settings which will place all settings in the **Startup.bas** file for easy configuration and entry as described next.

When loading and programming is complete, the Seehau main window opens (Figure 10).

Seehau will load its configuration from the settings specified in the Config program.

As shown in Figure 10, the initial Seehau screen defaults to address 400 in the source display, all registers are displayed in the window at right with the PC set to 400 by default. A data window is shown at the bottom with the memory contents at address 400. When a program is loaded, it will be loaded at the address specified in the .elf file from the compiler and the initial PC in the debugger will be set to the value specified in the **Config emulator-> Misc Setup** menu (which we have not covered yet).

# **B** Using MicroBlaze Trace

The EMUL-MICROBLAZE-PC provides a 512 or 2K deep trace with a trigger, post trigger count and break control. Probe Pins may be either 8 or 40-bits wide. It will display data connected to it as specified in the MHS file of Xilinx Platform Studio (XPS).

The Trace is triggered by an event specified in the **Event Configuration** window which is selected from the **Config** menu by selecting **Trace**. The **Event Configuration** window opens displaying the Events tab. (Figure 22).

| Event Configuration                                                                                                                                                    |                                                                                                                                                                                                                                                                        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Program Address, Register Program Address Trigger Condition Address Register Write Trigger Condition Reg Number Reg Value When both conditions enabled AND is implied. | and Probe Pins conditions are ORed<br>8 and 32 Probe Pins Trigger Conditions<br>Probe Pins (Channel A [70] Trigger Condition<br>Value[310] Enable<br>Care Mask FF<br>Mask upper 8 address lines to display as Channel A<br>MSBLSB FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF |

| Post Trigger Count<br>0<br>F Break Emulator on Trace Stop                                                                                                              | Value[310] Enable<br>Care Mask 00000000                                                                                                                                                                                                                                |

Figure 22. Event Configuration Window Displaying the Events Tab

### Events Tab

Events to trigger the trace may be specified on the basis of execution addresses, register accesses "anded" with the register value, or data values sensed by the "logic probe". The logic probe is an abstraction used to refer to signals connected to the Nohau debug core as specified in the MHS file of your project. The analogy to the probe pins of a logic analyzer is complete and Seehau refers to "probe pins" as if they were physically arranged in a row, even though they are actually signals in the FPGA fabric connected to the Nohau debug IP.

## **Trigger Conditions**

On the display, trigger conditions that are specified in separate outline "gray boxes" on the display are logically or'ed together and conditions within the same box are logically anded together. Some examples will be given later to help clarify the various conditions.

#### Program Address Trigger Condition

The value in the **Address** is the value that trigger is set to.

The **Enable check box** makes the trigger active.

If only a simple address is specified, the occurrence of that address will trigger the trace. If for example a register write trigger condition is specified also, then an "or" condition is implied which results in a trigger from the condition that occurs first.

#### **Register Write Trigger Condition**

Register Number is a number from 0 to 31 representing the 32 registers in MicroBlaze.

Register Value is a 32-bit Hex value contained in a register.

If both values are specified and enabled, an "and" is implied which means the trigger will happen when that specific register is written with the value specified.

## Probe Pins Channel A [7..0] Trigger Condition

Value [31 .. 0] is any 32-bit data value containing the 8 bit value we wish to trigger on.

Care Mask is an 8 bit mask that allows you to specify which of the 8 bit in the 32-bit word you wish to trigger on.

Mask upper address lines to display is a mask to specify if we want to use the upper 8 bits of the address field of the internal BRAM for the 8 bit probe. This is a mechanism to conserve BRAM on board the FPGA and is normally not used.

For example, if the value is specified as 12345678 and the care mask is 000000FF, then the trigger will be on the value 78 in the most significant bits of the data. For a mask of 0000FF00, the value would be 56. Remember MicroBlaze is a Big Endian machine.

## Probe Pins Channel B[31..0] Trigger Condition

These pins are optionally present because the additional channels require more on board BRAM for operation. It requires 4 on board ram for the trace but results in a trace that is 40-bits wide and 2K deep. It is included in a project by specifying the 32-bit version of the Nohau IP in the XPS pcores directory of your project. This is normally accomplished by simply renaming the debugtraceblaze file and the debugtraceblaze32 file. Whenever the BRAM is available, it is recommended that the additional 32-bit probe be included.

Value[31..0] is any 32-bit data value you would like to trigger on when enabled.

Care Mask is a 32-bit mask specified in hexadecimal, where a 1 implies a care bit and a 0 a don't care. This provides a powerful capability to trigger on a single bit or combination of bits in a 40-bit field.

If both 8 bit and 32-bit conditions are specified, then there is an implied "and" which means all 40bits must be true to cause a trigger.

#### Post Trigger Count

The frames to capture after the trigger condition has occurred are specified here. When the Post Trigger Count is zero, the trace will stop. When the post trigger count is 100, you will record an additional 100 frames after the trigger.

#### Break on Trace Stop

When checked, will cause emulation to break when the trace has stopped. This breakpoint has the additional feature of utilizing on-chip hardware breakpoints, which allows operation of trace breakpoints in ROM or Flash sections of memory.

#### Buttons Common to All Tabs

- **OK**: Saves the settings for the tab and exits the dialog box.

- **Apply**: Saves the settings for the tab.

- **Cancel**: Exits without saving the settings for the dialog box.

- Help: Displays the Seehau Help file.

- **Refresh**: Allows you to retrieve and view the current event configuration settings.

#### Trace Display Window

The **Trace Display** window is used to display data from trace capture. The default fields displayed from left to right are the **Frame, Address, Opcode, Instruction** and **Symbol**. The display can be activated by clicking on the blue button marked **TR** on the upper tool bar or via the **New** menu by selecting **New Trace Window**. There is no theoretical limit to the number of windows allowed.

The **Trace Display** window can display trace only (assembly), mixed (source and assembly) or source only. The mixed mode is shown in Figure 23.

| 💷 Trac  | e_1           |                 |                |             |        |          |

|---------|---------------|-----------------|----------------|-------------|--------|----------|

| Frame   | Address       | Opcode          | Instr.         |             | Symbol |          |

| -22     | 434           | 0000E1C4        | lhu            | r7,r1,r0    |        |          |

| -21     | 438           | OEOOCOF4        | shi            | r6,r0,#0xE  |        |          |

| -20     | 43C           | OACOEOF4        | shi            | r7,r0,#0xA  |        |          |

| -19     | 4C0           | 01008320        | addi           | r4,r3,#0x1  |        |          |

| -18     | 4C4           | 080093F8        | swi            | r4,r19,#0x8 |        |          |

| -17     | 4C8           | DCFF00B8        | bri            | #0x4A4      |        |          |

| -16     | j++;          |                 |                |             |        |          |

| -16     | 4CC           | OC0073E8        | lwi            | r3,r19,#0xC |        |          |

| -15     | 4DO           | 01008320        | addi           | r4,r3,#0x1  |        |          |

| -14     | 4D4           | 0C0093F8        | swi            | r4,r19,#0xC |        |          |

| -13     | *(leds)       | = j;            |                |             |        |          |

| -13     | 4D8           | 009860C8        | lw             | r3,r0,r19   |        |          |

| -12     | 4DC           | OC0093E8        | lwi            | r4,r19,#0xC |        |          |

| -11     | 4E0           | 001880D8        | SW             | r4,r0,r3    |        |          |

| -10     | 4F4           | 08000FB6        | rtsd           | r15,0x8     |        | -        |

| -9<br>∢ | 4F8           | 00000080        | nop            |             |        | <b>±</b> |

|         |               |                 |                |             |        | ► T      |

| MIXED g | ot frames Fra | ames:29(-29:-1) | , Trig Count:0 |             |        |          |

Figure 23. Trace Display in Mixed Mode

**Trace display options** are displayed by right clicking in the trace window to yield the display in Figure 24 below.

In the options list, select **Show Pod Pins** to display the probe signals in the next column of the display as shown for an 8-bit probe in Figure 24 below.

In the options list, select **Show Pod Pins** as to display the probe signals in the next column of the display as shown for a 32-bit probe in Figure 25 below. You may choose to display in Hex and the MSB first or LSB first.

| Frame                                    | Address                         | Opcode                                                                           | Instr.                           |                                                                                            | Symbol                                                                                                     |                        |

|------------------------------------------|---------------------------------|----------------------------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------|

| -11<br>-10<br>-9<br>-8<br>-7<br>-6<br>-5 | 4C0<br>4D4<br>4D8<br>4DC<br>4E0 | BC720008<br>B8000014<br>E8730010<br>20830001<br>F8930010<br>E8730004<br>E8930010 | bri<br>lwi<br>addi<br>swi<br>lwi | <pre>r18,0x8 #0x4D4 r3,r19,#0: r4,r3,#0x r4,r19,#0: r3,r19,#0: r3,r19,#0: r4,r19,#0:</pre> | Go to Frame number<br>Find Trigger Point<br>Zero Time at Cursor<br>Synchronize Source Wind<br>Display mode | Ctrl+Z<br>dow          |

| -4<br>-3<br>-2<br>-1                     | 4EC<br>4A0<br>4A8               | D8801800<br>B800FFB4<br>B8000008<br>F813000C                                     | bri<br>bri<br>swi                | r4,r0,r3<br>#0x4A0<br>#0x4A8<br>r0,r19,#0:                                                 | Find<br>Find Next<br>Find Previous<br>Show Source Line<br>Bookmarks<br>File                                | Ctrl+F<br>F3<br>Alt+F3 |

| 6<br>7<br>8 •<br><] ····                 | int i,<br>*(leds                | j;<br>_oe) = 0;<br>· 0800738                                                     | ° P                              | 1                                                                                          | Show Pod Pins<br>Show Pod Pins as<br>Show Data<br>Show Status<br>Show Symbol<br>All Options                |                        |

| 0000                                     | 00400 21 7                      | <u> </u>                                                                         | 20 40 05                         | 30 20 20 0:                                                                                | Trace Config<br>Settings<br>Change Caption                                                                 |                        |

Figure 24. Trace Display Pop-Up Window

| Frame | Address | Opcode      | Instr. |                | Pod  | Pins | Symbol | - |

|-------|---------|-------------|--------|----------------|------|------|--------|---|

| -11   |         | BC720008    |        | r18,0x8        | 0000 | 0000 | di di  |   |

| -10   | 4C0     | B8000 Opcor | de ri  | #0x4D4         | 0000 | 0000 |        |   |

| -9    | 4D4     | E8730010    | lwi    | r3, r19, #0x10 | 0000 | 0000 |        |   |

| -8    | 4D8     | 20830001    | addi   | r4,r3,#0x1     | 0000 | 0000 |        |   |

| -7    | 4DC     | F8930010    | swi    | r4, r19, #0x10 | 0000 | 0000 |        |   |

| -6    | 4E0     | E8730004    | lwi    | r3, r19, #0x4  | 0000 | 0000 |        |   |

| -5    | 4E4     | E8930010    | lwi    | r4, r19, #0x10 | 0000 | 0000 |        |   |

| -4    | 4E8     | D8801800    | SW     | r4,r0,r3       | 0000 | 0000 |        |   |

| -3    | 4EC     | B800FFB4    | bri    | #0x4A0         | 0000 | 0000 |        |   |

| -2    | 4A0     | B8000008    | bri    | #0x4A8         | 0000 | 0000 |        |   |

| -1    | 4A8     | F813000C    | swi    | r0,r19,#0xC    | 0000 | 0000 |        | 1 |

| <     |         |             |        |                |      |      |        | > |

Figure 25. Trace Display with 8 bit Probe in Binary

| Frame   | Address  | Opcode     | Instr.     |                 | Pod  | Pins |      |                                         |         |

|---------|----------|------------|------------|-----------------|------|------|------|-----------------------------------------|---------|

| -8      | 488      | 2060A000   | addi       | r3,r0,#0xA000   | 0000 | 0000 | 0000 | 000000000000000000000000000000000000000 | 1110000 |

| -7      | 48C      | F8730004   | swi        | r3, r19, #0x4   | 0000 | 0000 | 1111 | 11111111111101000000                    | 0000000 |

| -6      | volatile | e int *led | is oe = 0: | kFFFFA004;      |      |      |      |                                         |         |

| -6      | 490      | 2060A004   | addi       | r3, r0, #0xA004 | 0000 | 0000 | 1111 | 11111111111101000000                    | 0000000 |

| -5      | 494      | F8730008   | swi        | r3,r19,#0x8     | 0000 | 0000 | 1111 | 11111111111101000000                    | 0000100 |

| -4      | *(leds o | be) = 0;   |            |                 |      |      |      |                                         |         |

| -4      | 498      | E8730008   | lwi        | r3, r19, #0x8   | 0000 | 0000 | 1111 | 11111111111101000000                    | 0000100 |

| -3      | 49C      | D8001800   | SW         | r0,r0,r3        | 0000 | 0000 | 1111 | 11111111111101000000                    | 0000100 |

| -2      | while (1 | L) {       |            |                 |      |      |      |                                         |         |

| -2      | 4A0      | B8000008   | bri        | #0x4A8          | 0000 | 0000 | 0000 | 000000000000000000000000000000000000000 | 0000000 |

| -1      | for (i=  | ; i<1000   | 000; i++)  | {};             |      |      |      |                                         |         |

| -1<br>< | 47.9     | F813000C   | owi        | rn r10 €nvr     | 0000 | 0000 | 0000 | 000000000000000000000000000000000000000 | 100100  |

Figure 26. Trace 40 bit Mixed Mode Display in Binary

| Frame | Address | Opcode   | Instr. |               | Po | d Pins   | Symbol |   |

|-------|---------|----------|--------|---------------|----|----------|--------|---|

| -10   | 480     | FA610014 | swi    | r19,r1,#0x14  | 00 | 000008F0 |        | ٦ |

| -9    | 484     | 02610000 | add    | r19,r1,r0     | 00 | 00000000 |        |   |

| -8    | 488     | 2060A000 | addi   | r3,r0,#0xA000 | 00 | 000008F0 |        |   |

| -7    | 48C     | F8730004 | swi    | r3, r19, #0x4 | 00 | FFFFA000 |        |   |

| -6    | 490     | 2060A004 | addi   | r3,r0,#0xA004 | 00 | FFFFA000 |        |   |

| -5    | 494     | F8730008 | swi    | r3, r19, #0x8 | 00 | FFFFA004 |        |   |

| -4    | 498     | E8730008 | lwi    | r3, r19, #0x8 | 00 | FFFFA004 |        |   |

| -3    | 49C     | D8001800 | SW     | r0,r0,r3      | 00 | FFFFA004 |        |   |

| -2    | 4A0     | B8000008 | bri    | #0x4A8        | 00 | 00000000 |        |   |

| -1    | 4A8     | F813000C | swi    | r0,r19,#0xC   | 00 | 000004A4 |        | • |

| <     |         |          |        |               |    |          |        | > |

Figure 27. Trace 40 bit Display in Hexadecimal

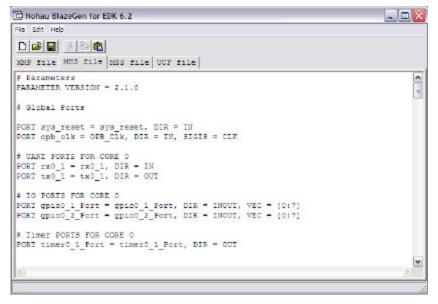

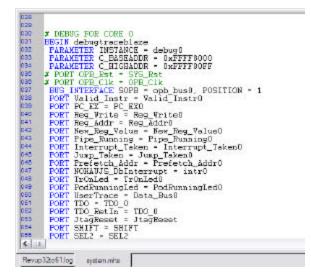

## BlazeGen for EDK 6.2 Projects

## BlazeGen

BlazeGen is a platform generator tool designed to accomplish two goals:

- 1. Build small known good projects for use in board power up and getting started exercises.

- 2. Adding Nohau debug tools to existing projects without hand editing numerous text files and recompiling numerous times. A procedure is provided in the next chapter to simplify the process.

The procedure for building a project with BlazeGen will be covered here. For using Base System Builder, see the procedure in the next section.

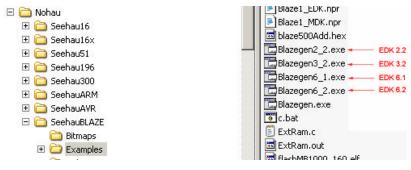

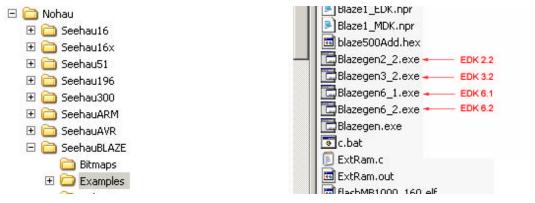

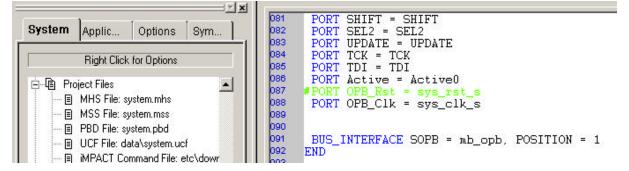

#### Invoke BlazeGen by Double-Clicking the correct .exe File in the Nohau Examples Directory

For 6.2 select BlazeGen6\_2.exe.

The application is located under the installed SeehauBlaze directory. Normally located on the hard disk at c:\nohau\seehaublaze\examples (Figure 28). You will need to select the correct version for the PLATFORM STUDIO version that you are using.

Figure 28. Directory Location

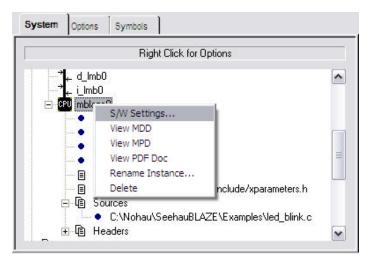

Then, use the **Edit -> CoresetUp** option in BlazeGen to begin your build (Figure 29).

|                | lohau BlazeG  | en for EDK (               | 6.2             |   |

|----------------|---------------|----------------------------|-----------------|---|

| File           | Edit Help     |                            |                 |   |

| <u></u><br>хмі | K Cut<br>Copy | Ctrl+X<br>Ctrl+C<br>Ctrl+V | 3 file UCF file |   |

|                | Copy NetLis   | t to EDK                   |                 | ~ |

|                | CoresetUp     |                            |                 |   |

|                | Add Debug     |                            |                 |   |

|                | Compile Net   | tLst                       | ]               |   |

| <              |               |                            |                 |   |

|                |               |                            |                 |   |

Figure 29. Core Setup via BlazeGen

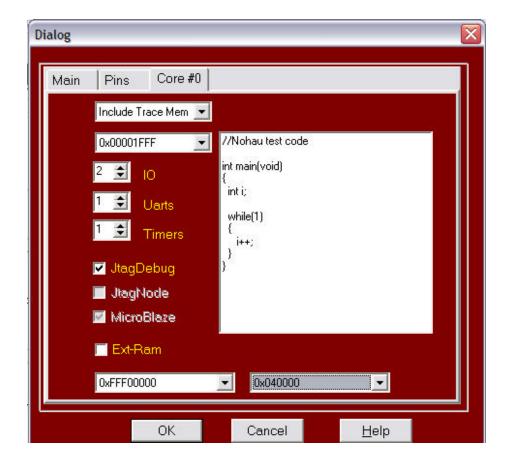

From the dialog in Figure 30, select as follows for your first small project.

| Dialog                                                                                                                                                                                                                                                                                                                                                                                                                                                          | X |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Main       Pins       Core #0       Core #1         Path       c:tyourpathname         Select Board         Nohau Virtex Eval       •         Nohau Virtex Eval       •         Nohau Virtex Eval       •         Nohau Spartan2E Eval       •         Insight Virtex Eval       •         Insight Spartan2E Eval       •         Insight V2ProV7       •         Browse for Other Boards       •         Clock       100000000         Reset Active       High |   |

| OK Cancel Help                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |

Figure 30. BlazeGen Main Setup

Enter a path for your directory or a new one 'yourname' as shown. Select your board from the list or browse to a list of all boards supported in EDK. For this example, EDK -> Board ->Memec\_Design ->Boards -> Memec\_Design\_V2P4 \_FG456\_Rev4\_P160\_Comm.

| Family Virtex2P |

|-----------------|

|-----------------|

- Device XC2VP4

- Speed Grade 6

- Clock 100Mhz

- Reset Active LOW

Cores 1

Select OK

Figure 31 below will pop up.

| Copy N   | let Lists         |                   |              | Σ |

|----------|-------------------|-------------------|--------------|---|

| (        | Copy Nohau I      | NETLISTS to       | EDK Path:    |   |

|          | c:\yourname\PCore | es\               |              |   |